ESD基本功能

ESD意思是“静电放电”,ESD电路用于芯片在受到静电放电时保护芯片不受物理损伤。ESD能力在芯片端和应用端的概念是不一样的,可以理解为芯片ESD和系统ESD,这是两个完全不一样的东西。

芯片ESD是指芯片在不带电时对芯片进行的ESD测试,芯片周围不接任何东西,测试的是芯片的泄放静电能力。

系统ESD是指整个系统(或者说模组)在带电时对系统进行的ESD抗干扰测试,芯片周围接了各种各样的器件,包括电阻,电容,电感,磁珠以及别的芯片,测试的是整个模组系统的抗干扰能力,通常分为接触放电和空气放电,接触放电一般高到8kV~10kV,空气放电一般高到15kV。

虽然都叫ESD能力,但完全是两个不一样的概念,包括测试方法,测试设备,测试目的,如何提升ESD能力的方法都不一样,很多人将这两个概念混淆。这里不对两个概念做深入展开,下面提到的ESD都是指芯片ESD能力。

ESD(静电放电)主要分为以下几种类型:

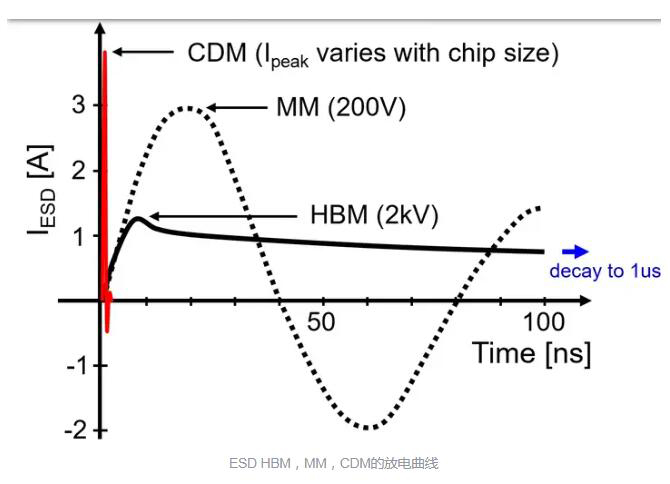

1)人体放电模型(Human Body Model,HBM):这是指人体在活动过程中积累静电,然后通过接触芯片放电。

2)机器放电模型(Machine Model,MM):由机器(例如自动化设备)产生的静电通哥接触芯片放电。

3)充电器件模型(Charged Device Model,CDM):指带静电的芯片在接触其他导体时发生的放电。

好的ESD电路需要有如下特征

-

正常上电不触发

芯片正常上电时不能触发ESD放电电路,因为ESD保护电路开启时,阻抗非常小,电流将会很大,所以正常上电时不能触发ESD电路。 -

发生静电事件时开启

当ESD静电注入时芯片时需要开启ESD 保护电路,并且要将电压始终钳位在击穿电压以下,防止芯片被静电产生的高压损坏。 - 性能指标

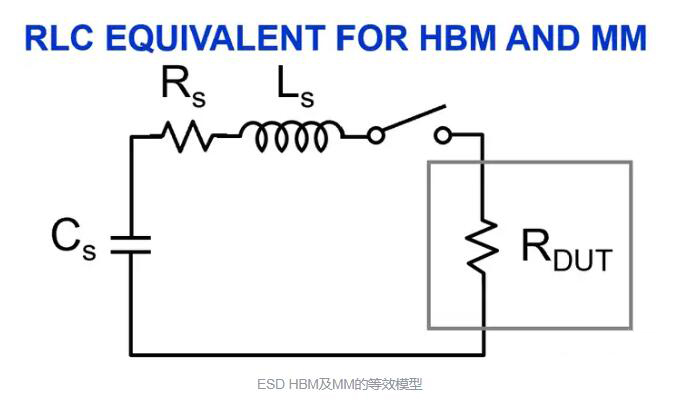

ESD放电模型

ESD 的等效模型以及放电如上图所示,在ESD 放电时电流可达几个安培甚至更高,所以ESD的放电路径要做得非常强壮,阻抗要做得非常小,所以你可以看到芯片的ESD环走线通常都很粗,VIA也打得很满,有时也看到ESD环用很厚的Top Metal来走线,目的就是降低ESD环路阻抗。

ESD 保护策略

上面提到发生ESD事件时,电流很大,如果没有设计好ESD保护电路,那电压可以上升到很高,从而损坏芯片;我们通常用以下几种电路来保护芯片。

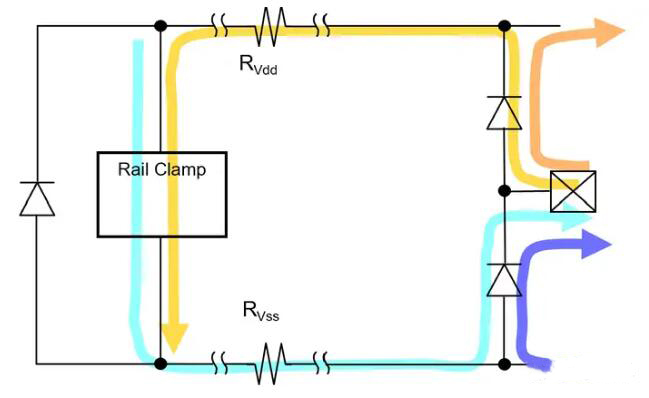

1)Diode+ Rail Clamp保护策略

使用Diode + Rail Clamp的保护方式在模拟芯片或模拟IO中使用比较多,因为Diode面积小,寄生电容小,对模拟IO友好,缺点是到地通路没有正向放电能力。

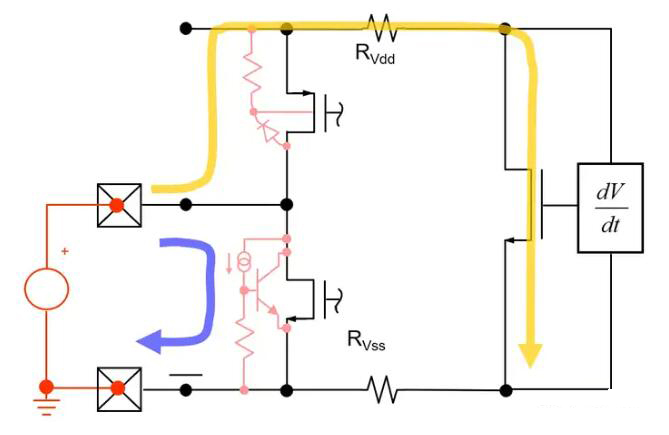

2)GGNMOS+ 寄生diode +Rail Clamp保护策略

使用GGNMOS + 寄生diode+ Rail Clamp的保护方式在MCU芯片或GPIO中使用最多,因为GPIO本身自带大的输出管,可以既当输出管使用,又当ESD放电管使用。

GGNMOS可以作为放电通路,寄生Diode+Rail Clamp也可以作为放电通路,在GGNMOS开启之前,电荷可以从寄生Diode+Rail Clamp通路走,电压上升后开启GGNMOS,电荷可以从两条通路走,从而增强泄放能力。缺点是寄生电容大,高温下漏电大,对模拟电路不友好。

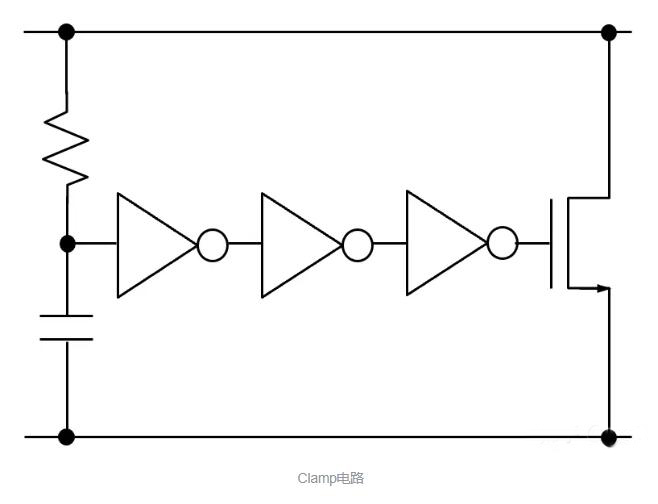

3)Clamp电路

通常电源VDD pad以及地VSS Pad可以做成Clamp电路,简单Clamp电路的示意图如下所示

Clamp的设计主要是RC的参数以及功率管的大小,根据ESD要求来决定功率管的大小以及在芯片中放Clamp个数的密度。

来源:知乎:恩泽