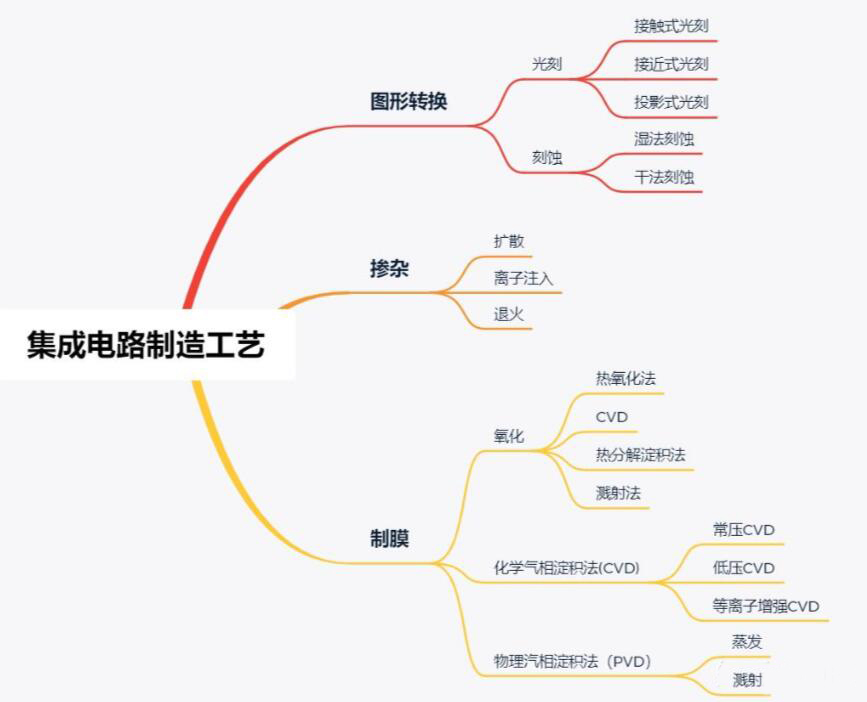

集成电路工艺主要包括如下几点内容:图形转换,掺杂,制膜。

- 图形转换:将设计在掩膜版上的图形转移到半导体晶片上,工艺主要包括光刻与刻蚀。 掺杂:根据设计需要,将各种杂质掺杂在需要的位置上,形成晶体管、接触等。

- 工艺主要包括离子注入、退火和扩散。

- 制膜:制作各种材料的薄膜,工艺主要包括氧化、CVD和PVD。

1.1 图形转换:光刻技术。

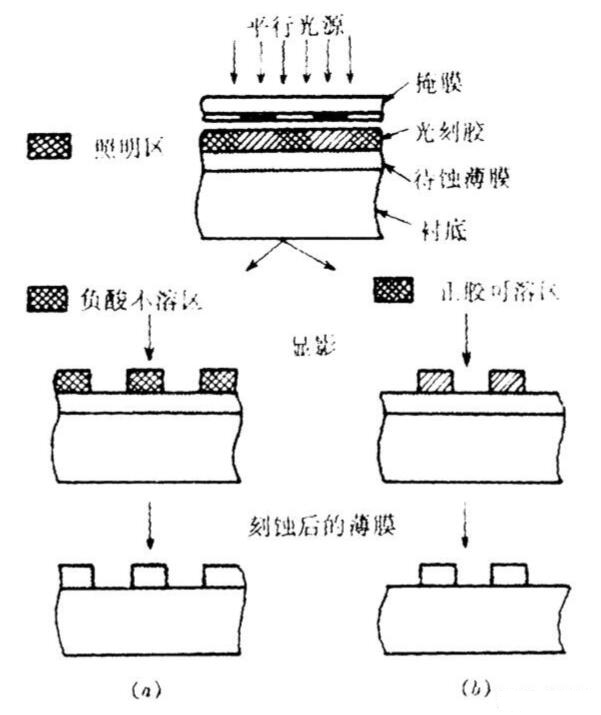

光刻三要素:光刻胶、掩膜版和光刻机。

光刻胶:又称光致抗蚀剂,受到特定波长光线的作用后,导致其化学结构发生变化,使光刻胶在某种特定溶液中的溶解特性改变。

正胶:曝光后可溶,分辨率高,在超大规模集成电路工艺中,一般只采用正胶。

负胶:曝光后不可溶,分辨率差,适用于加工线宽≥3us的线条。

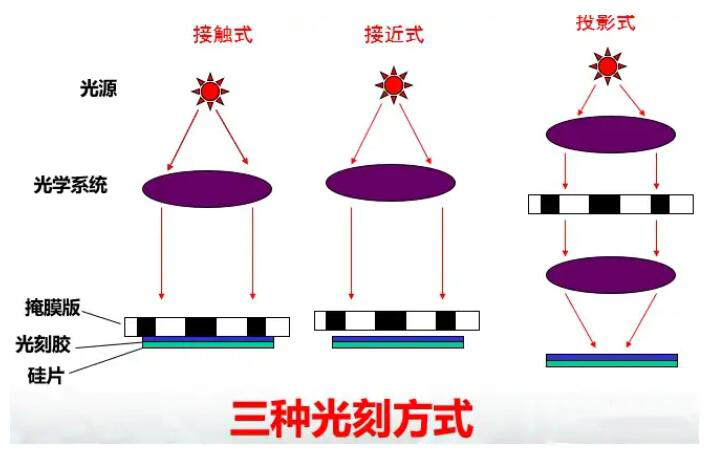

几种常见的光刻方法:

- 接触式光刻:分辨率较高,但是容易造成掩膜版和光刻胶膜损失。

- 接近式曝光:在硅片和掩膜版之间有一个很小的间隙(10-25um),可以大大减小膜版的损伤,分辨率较低。

- 投影式曝光:利用透镜或反射镜将掩膜版上的图形投影到衬底上的曝光方法,目前用的最多曝光方式。

超细线条光刻技术

- 1:甚远紫外线(EUV)

- 2:电子束光刻:

- 3:X射线

- 离子束光刻

1.2 图形转换:刻蚀技术。

湿法刻蚀:利用液态化学试剂或溶液通过化学反应进行刻蚀的方法。

- 1:应用:磨片、抛光、清洗和腐蚀。

- 2:优点:选择性好、重复性好、生产率高、设备简单、成本低:

- 3:缺点:钻蚀严重,对图形的控制性差。

干法刻蚀:利用低压放电产生的等离子体中的离子或游离基(处于激发态的分子、原子及各种原子基团等)与材料发生化学反应或通过轰击等物理作用而达到刻蚀的目的。

- 1:溅射与离子束刻蚀

- 2:等离子刻蚀

- 3:反应例子刻蚀

2. 掺杂:将需要的杂质掺入特定的半导体区域中,以达到改变半导体电学性质,形成PN结、电阻和欧姆接触。磷或砷形成N型硅,硼形成P型硅。

2.1 扩散

- 主要是III和V族元素

- 一般要在很高的温度(950-1280℃)进行

- 磷、硼、砷在二氧化碳层中扩散系数均远小于在硅中的扩散系数,可以利用氧化层作为杂质扩散的掩蔽层。

2.2 离子注入:将具有很高能量的杂质离子射入半导体衬底中的掺杂技术,掺杂深度由注入杂质离子的能量和质量决定,掺杂浓度由注入杂质离子的数目(剂量)决定。

- 掺杂均匀性好;

- 温度低:小于600℃

- 可精确控制杂质分布

- 可注入各种各样元素

- 横向扩展比扩散小的多。

- 可以对化合物半导体进行掺杂

2.3 退火,也叫热处理,集成电路工艺中所有的在氮气不活泼气氛中进行的热处理过程,称为退火。退火方式有炉退火,快速退火。

- 激活杂质,使不在晶格位置上的离子运动到晶格位置,以便具有电活性,产生自由载流子,起到杂质作用。

- 消除损伤。

3.1 制模:氧化工艺

制备SiO2层:十分理想的电绝缘材料,化学性质非常稳定。常作为MOS器件的绝缘栅介质,扩散时的掩蔽层,隔离介质材料,电容器绝缘介质材料,钝化材料等。

SiO2制备方法:热氧化法,化学气相淀积法、热分解淀积法、溅射法

3.2 制模:化学汽相淀积(CVD),通过气态物质的化学反应在衬底上淀积一层薄膜材料的过程。

方法:常压化学汽相淀积;低压化学汽相淀积;等离子增强化学汽相淀积。

举例1:单晶硅的化学汽相淀积(外延):一般,将在衬底上生产单晶材料的工艺叫做外延,生长有外延层的晶体片叫做外延片。

举例2:二氧化硅的化学汽相淀积:可以作为金属化时的介质层,还可以作为离子注入或扩散的掩蔽膜。

3.3 制模:物理汽相淀积(PVD)

蒸发:真空系统中,金属原子获得足够能量后,便可以脱离表面的束缚成为蒸汽原子,淀积在晶片上。

溅射:真空系统中充入惰性气体,在高压电场作用下,气体放电形成的离子被强电场加速,轰击靶材料,使靶原子逸出并被溅射到晶片上。